ASN Filter Designer’s ANSI C SDK framework, provides developers with a comprehensive C code framework for developing AIoT filtering application on microcontrollers and embedded platforms. Although the framework has been primarily designed to support the just ASN filter Designer’s filter cascade, it is possible to create extra filter objects to augment the cascade. Two common filtering methods used by AIoT developers are the Median and moving average (MA) filters. Although these fully integrated within the Framework’s filter cascade, it is often useful to have the flexibility of an additional filtering block to act as a post filter smoothing filter. An extra median or MA filter may be easily added to The Median filter is non-linear filtering method that uses the concept of majority voting (i.e. calculating the median) to remove glitches and smooth data. It is edge preserving, making it a good choice for enhancing square waves or pulse like data. MedianFilter_t MyMedianfilter; InitMedianFilter(&MyMedianfilter,7); // median of length 7 for (n=0; n<TEST_LENGTH_SAMPLES; n+=4) MedianFilterData(&MyMedianfilter,InputTemp, OutputTemp); OutputValues[n]=OutputTemp[0]; [/code] The moving average (MA) filter is optimal for reducing random noise while retaining a sharp step response, making it a versatile building block for smart sensor signal processing applications. It is perhaps one of the most widely used digital filters due to its conceptual simplicity and ease of implementation. MAFilter_t MyMAfilter; InitMAFilter(&MyMAfilter,9); // MA of length 9 for (n=0; n<TEST_LENGTH_SAMPLES; n+=4) MAFilterData(&MyMAfilter,InputTemp, OutputTemp); OutputValues[n]=OutputTemp[0]; [/code]main.c as shown below. Notice that data is filtered in blocks of 4 as required by the framework.Median filter

[code language=”cpp”]

#include "ASN_DSP/DSPFilters/MedianFilter.h"

float InputTemp[4];

float OutputTemp[4];

{

InputTemp[0]=InputValues[n];

InputTemp[1]=InputValues[n+1];

InputTemp[2]=InputValues[n+2];

InputTemp[3]=InputValues[n+3];

OutputValues[n+1]=OutputTemp[1];

OutputValues[n+2]=OutputTemp[2];

OutputValues[n+3]=OutputTemp[3];

}

Moving Average filter

[code language=”cpp”]

#include "ASN_DSP/DSPFilters/MAFilter.h"

float InputTemp[4];

float OutputTemp[4];

{

InputTemp[0]=InputValues[n];

InputTemp[1]=InputValues[n+1];

InputTemp[2]=InputValues[n+2];

InputTemp[3]=InputValues[n+3];

OutputValues[n+1]=OutputTemp[1];

OutputValues[n+2]=OutputTemp[2];

OutputValues[n+3]=OutputTemp[3];

}

Posts

Finite impulse response (FIR) filters are useful for a variety of sensor signal processing applications, including audio and biomedical signal processing. Although several practical implementations for the FIR exist, the Direct Form Transposed structure offers the best numerical accuracy for floating point implementation. However, when considering fixed point implementation on a micro-controller, the Direct Form structure is considered to be the best choice by virtue of its large accumulator that accommodates any intermediate overflows.

This application note specifically addresses FIR filter design and implementation on a Cortex-M based microcontroller with the ASN Filter Designer for both floating point and fixed point applications via the Arm CMSIS-DSP software framework. Details are also given (including an Arm reference software pack) regarding implementation of the FIR filter in Arm/Keil’s MDK industry standard Cortex-M micro-controller development kit.

Introduction

ASN Filter Designer provides engineers with a powerful DSP experimentation platform, allowing for the design, experimentation and deployment of complex FIR digital filter designs for a variety of sensor measurement applications. The tool’s advanced functionality, includes a graphical based real-time filter designer, multiple filter blocks, various mathematical I/O blocks, live symbolic math scripting and real-time signal analysis (via a built-in signal analyser). These advantages coupled with automatic documentation and code generation functionality allow engineers to design and validate a digital filter within minutes rather than hours.

The Arm CMSIS-DSP (Cortex Microcontroller Software Interface Standard) software framework is a rich collection of over sixty DSP functions (including various mathematical functions, such as sine and cosine; IIR/FIR filtering functions, complex math functions, and data types) developed by Arm that have been optimised for their range of Cortex-M processor cores.

The framework makes extensive use of highly optimised SIMD (single instruction, multiple data) instructions, that perform multiple identical operations in a single cycle instruction. The SIMD instructions (if supported by the core) coupled together with other optimisations allow engineers to produce highly optimised signal processing applications for Cortex-M based micro-controllers quickly and simply.

ASN Filter Designer fully supports the CMSIS-DSP software framework, by automatically producing optimised C code based on the framework’s DSP functions via its code generation engine.

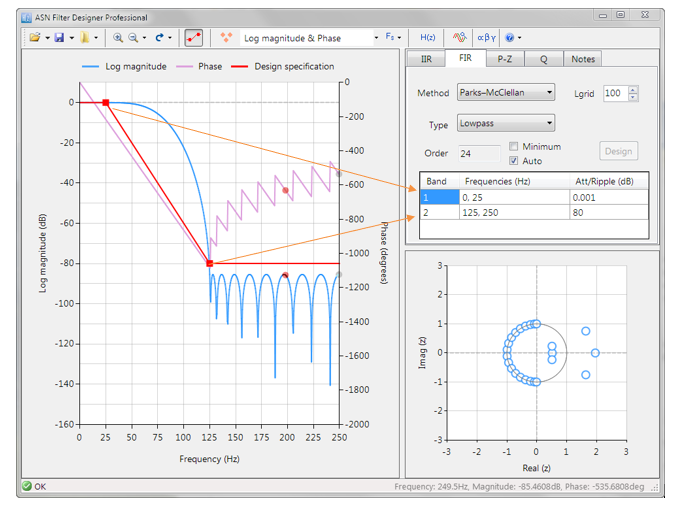

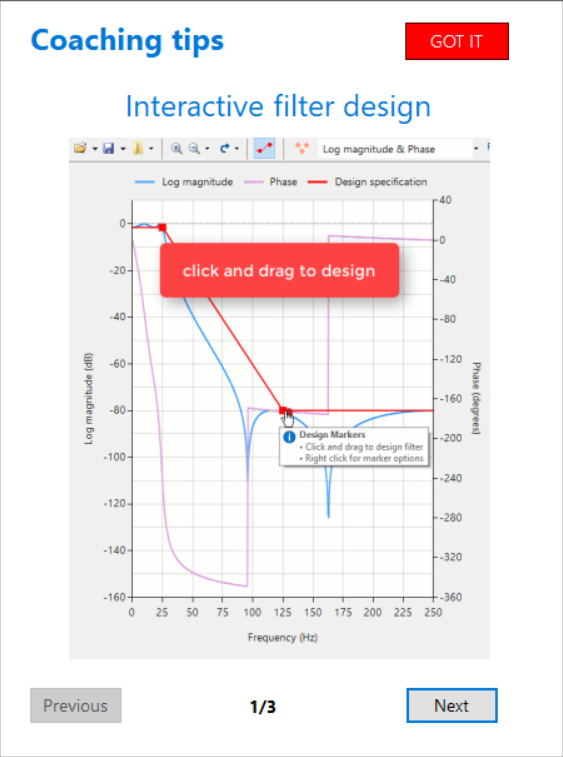

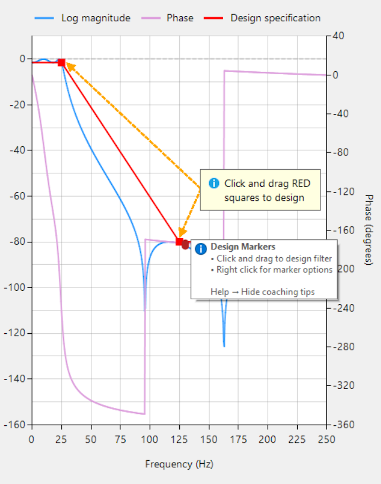

Designing FIR filters with the ASN Filter Designer

ASN Filter Designer provides engineers with an easy to use, intuitive graphical design development platform for FIR digital filter design. The tool’s real-time design paradigm makes use of graphical design markers, allowing designers to simply draw and modify their magnitude frequency response requirements in real-time while allowing the tool automatically fill in the exact specifications for them.

Consider the design of the following technical specification:

| Fs: | 500Hz |

| Passband frequency: | 0-25Hz |

| Type: | Lowpass |

| Method: | Parks-McClellan |

| Stopband attenuation @ 125Hz: | ≥ 80 dB |

| Passband ripple: | < 0.01dB |

| Order: | Small as possible |

Graphically entering the specifications into the ASN Filter Designer, and fine tuning the design marker positions, the tool automatically designs the filter), automatically choosing the required filter order, and in essence – automatically producing the filter’s exact technical specification!

The frequency response of a filter meeting the specification is shown below:

This Lowpass filter will form the basis of the discussion presented herein.

Parks–McClellan algorithm

The Parks–McClellan algorithm is an iterative algorithm for finding the optimal Chebyshev FIR filter. The algorithm uses an indirect method for finding the optimal filter coefficients, that offers a degree of flexibility over other FIR design methods, in that each band may be individually customised in order to suit the designer’s requirements.

The primary FIR filter designer UI implements the Parks-McClellan algorithm, allowing for the design of the following filter types:

| Filter Types | Description |

| Lowpass | Designs a lowpass filter. |

| Highpass | Designs a highpass filter. |

| Bandpass | Designs a bandpass filter. |

| Bandstop | Designs a bandstop filter. |

| Multiband | Designs a multiband filter with an arbitrary frequency response. |

| Hilbert transformer | Designs an all-pass filter with a -90 degree phase shift. |

| Differentiator | Designs a filter with +20dB/decade slope and +90 degree phase shift. |

| Double Differentiator | Designs a filter with +40dB/decade slope and a +90 degree phase shift. |

| Integrator | Designs a filter with -20dB/decade slope and a -90 degree phase shift. |

| Double Integrator | Designs a filter with -40dB/decade slope and a -90 degree phase shift. |

These ten filter types provide designers with a great deal of flexibility for a variety of IoT applications. Design requirements may be simply specified via the use of the design markers. In all cases, the tool will automatically calculate the required filter order to meet the designer’s specification.

The Parks-McClellan algorithm is an optimal Chebyshev FIR design method. However, the algorithm may not converge for some specifications. In such cases, increasing the distance between the design marker bands generally helps.

Other FIR design methods

Designers looking to experiment with other types of FIR design methods may use the ASN FilterScript live symbolic math scripting language. The scripting language supports over 65 scientific commands and provides designers with a familiar and powerful programming language, while at the same time allowing them to implement complex symbolic mathematical expressions. The following functions are supported:

| Function | Description |

| movaver | Moving average FIR filter design. |

| firwin | FIR filter design based on the Window method. |

| firarb | Designs an FIR Window based filter with an arbitrary magnitude response. |

| firkaiser | Designs an FIR filter based on the Kaiser window method. |

| firgauss | Designs an FIR Gaussian lowpass filter. |

| savgolay | Design an FIR Savitzky-Golay lowpass smoothing filter. |

Please refer to the ASN FilterScript reference guide for more details.

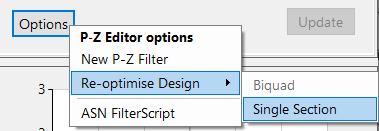

All filters designed in ASN FilterScript are designed using double precision arithmetic in the H2 filter sandbox. An H2 filter must be transformed to an H1 (primary) filter for deployment.

This may be simply achieved via the P-Z options menu:

The re-optimise method automatically analyses and converts the H2 filter into an H1 filter.

Floating point implementation

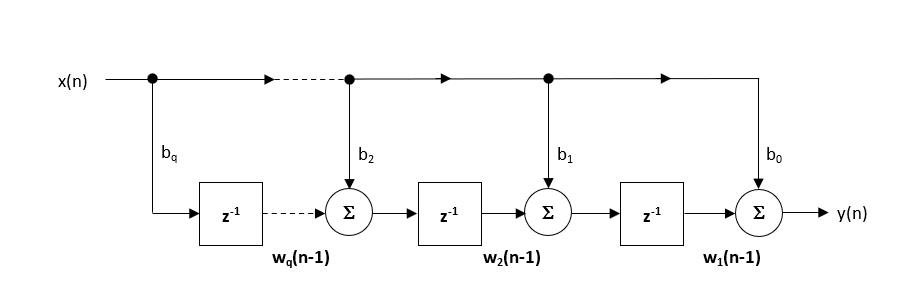

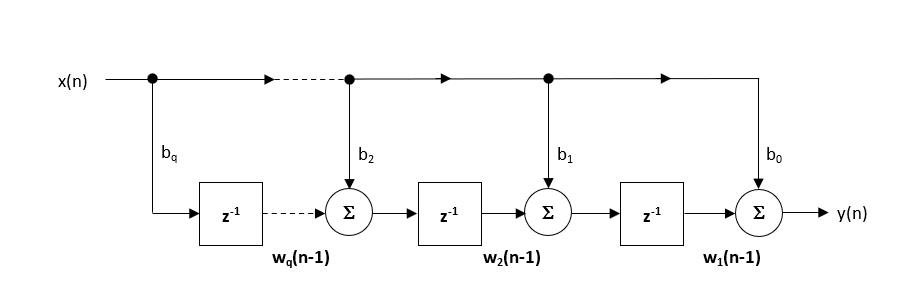

When implementing a filter in floating point (i.e. using double or single precision arithmetic) the Direct Form Transposed structure is considered the most numerically accurate. This can be readily seen by analysing the difference equations below (used for implementation), as the undesirable effects of numerical swamping are minimised, since floating point addition is performed on numbers of similar magnitude.

\(\displaystyle \begin{eqnarray}y(n) & = &b_0x(n) &+& w_1(n-1) \\ w_1(n)&=&b_1x(n) &+& w_2(n-1) \\ w_2(n)&=&b_2x(n) &+& w_3(n-1) \\ \vdots\quad &=& \quad\vdots &+&\quad\vdots \\ w_q(n)&=&b_qx(n) \end{eqnarray}\)

\(\displaystyle \begin{eqnarray}y(n) & = &b_0x(n) &+& w_1(n-1) \\ w_1(n)&=&b_1x(n) &+& w_2(n-1) \\ w_2(n)&=&b_2x(n) &+& w_3(n-1) \\ \vdots\quad &=& \quad\vdots &+&\quad\vdots \\ w_q(n)&=&b_qx(n) \end{eqnarray}\)

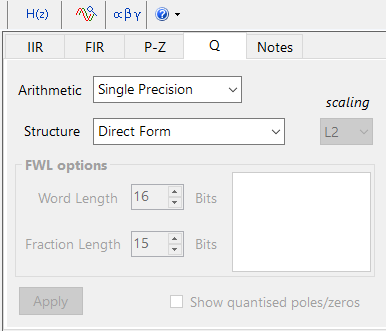

The quantisation and filter structure settings used to implement the FIR can be found under the Q tab (as shown below).

Despite the Direct Form Transposed structure being the most efficient for floating point implementation, the Arm CMSIS-DSP library does not currently support the Direct Form Transposed structure for FIR filters. Only the Direct Form structure is supported.

Setting Arithmetic to Single Precision and Structure to Direct Form and clicking on the Apply button configures the FIR considered herein for the CMSIS-DSP software framework.

The optimised functions within the Arm CMSIS-DSP framework currently support Single Precision arithmetic only.

Support for Double Precision and the Direct Form Transposed structure will be added in future releases.

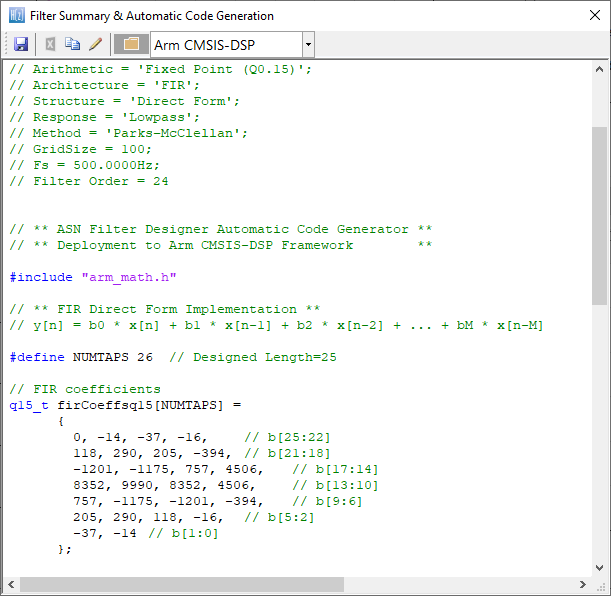

Fixed point implementation

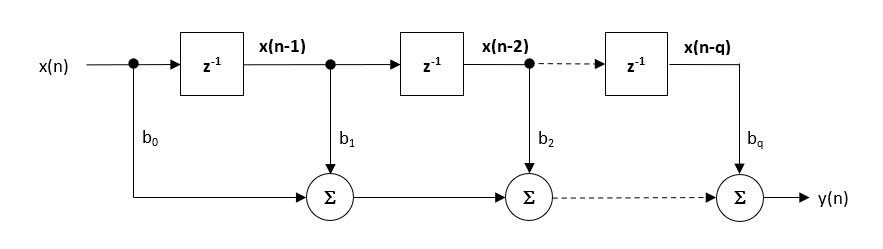

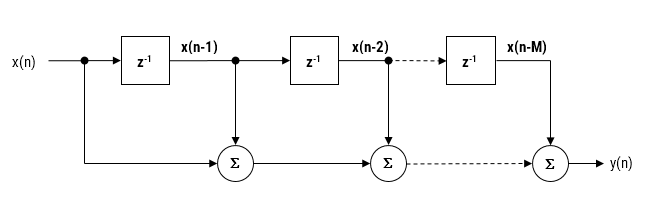

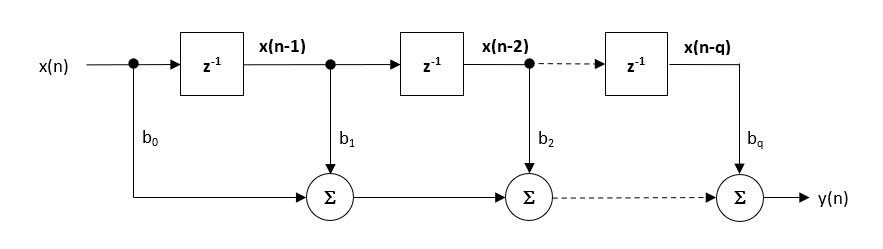

When implementing a filter with fixed point arithmetic, the Direct Form structure is considered to be the best choice by virtue of its large accumulator that accommodates any intermediate overflows. The Direct Form structure and associated difference equation are shown below.

\(\displaystyle y(n) = b_0x(n) + b_1x(n-1) + b_2x(n-2) + …. +b_qx(n-q) \)

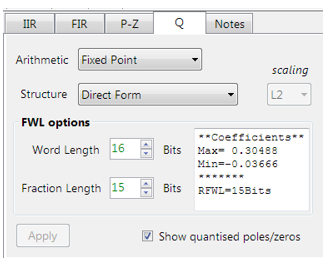

The CMSIS-DSP Framework supports Q7, Q15 and Q31 coefficient quantisation only. The options may be simply specified via the quantisation tab Q as shown below:

The tool’s inbuilt analytics (shown in the textbox) are intended to help the designer choose the most suitable quantisation settings.

As seen on the left, the tool has recommended a RFWL (recommended fraction length) of 15bits (Q15) for the coefficients, which is as required.

The Direct form structure is chosen over the Direct Form Transposed as a single (40-bit) accumulator can be used. The tool’s automatic code generator makes use of CMSIS-DSP’s 64-bit accumulators functions, so that the final C code deployed to a Cortex-M device will not overflow.

Deploying Arm CMSIS-DSP compliant code

The ASN Filter Designer’s automatic code generation engine facilitates the export of a designed filter to Cortex-M Arm based processors via the Arm CMSIS-DSP software framework. The tool’s built-in analytics and help functions assist the designer in successfully configuring the design for deployment.

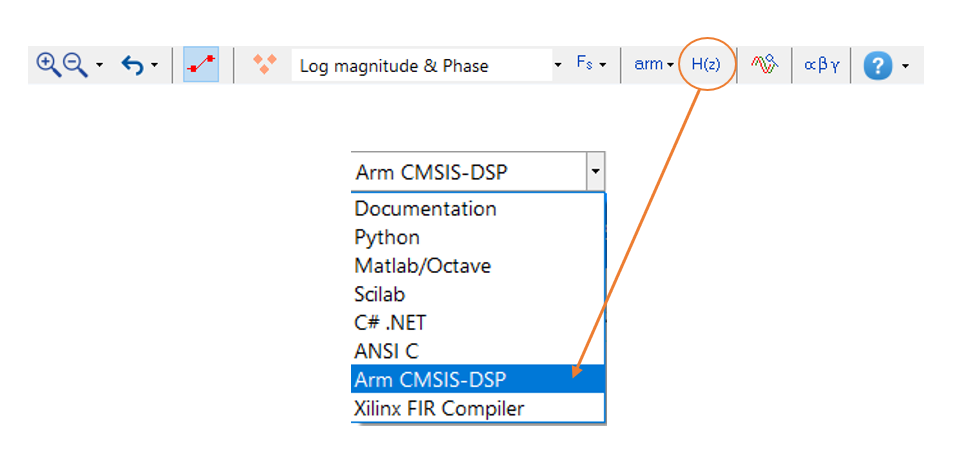

Select the Arm CMSIS-DSP framework from the selection box in the filter summary window:

The automatically generated C code based on the Arm CMSIS-DSP framework for direct implementation on an Arm based Cortex-M processor is shown below:

This code may be directly used in any Cortex-M based development project.

Arm Keil’s MDK (uVision)

As mentioned above, the code generated by the Arm CMSIS DSP code generator may be directly used in any Cortex-M based development project tooling, such as Arm Keil’s industry standard uVision MDK (micro-controller development kit).

The following Arm software pack is available on Keil’s website for using this code directly with Keil uVision MDK.

As discussed in a previous article, the moving average (MA) filter is perhaps one of the most widely used digital filters due to its conceptual simplicity and ease of implementation. The realisation diagram shown below, illustrates that an MA filter can be implemented as a simple FIR filter, just requiring additions and a delay line.

Modelling the above, we see that a moving average filter of length \(\small\textstyle L\) for an input signal \(\small\textstyle x(n)\) may be defined as follows:

\( y(n)=\large{\frac{1}{L}}\normalsize{\sum\limits_{k=0}^{L-1}x(n-k)}\quad \text{for} \quad\normalsize{n=0,1,2,3….}\label{FIRdef}\tag{1}\)

This computation requires \(\small\textstyle L-1\) additions, which may become computationally demanding for very low power processors when \(\small\textstyle L\) is large. Therefore, applying some lateral thinking to the computational challenge, we see that a much more computationally efficient filter can be used in order to achieve the same result, namely:

\(H(z)=\displaystyle\frac{1}{L}\frac{1-z^{-L}}{1-z^{-1}}\tag{2}\label{TF}\)

with the difference equation,

\(y(n) =y(n-1)+\displaystyle\frac{x(n)-x(n-L)}{L}\tag{3}\)

Notice that this implementation only requires one addition and one subtraction for any value of \(\small\textstyle L\). A further simplification (valid for both implementations) can be achieved in a pre-processing step prior to implementing the difference equation, i.e. scaling all input values by \(\small\textstyle L\). If \(\small\textstyle L\) is a power of two (e.g. 4,8,16,32..), this can be achieved by a simple binary shift right operation.

Is it an IIR or actually an FIR?

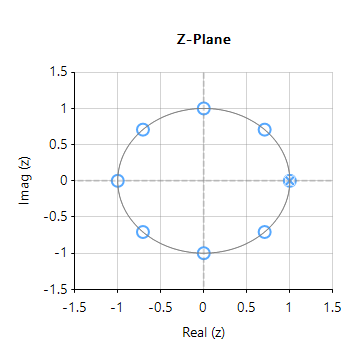

Upon initial inspection of the transfer function of Eqn. \(\small\textstyle\eqref{TF}\), it appears that the efficient Moving average filter is an IIR filter. However, analysing the pole-zero plot of the filter (shown on the right for \(\small\textstyle L=8\)), we see that the pole at DC has been cancelled by a zero, and that the resulting filter is actually an FIR filter, with the same result as Eqn. \(\small\textstyle\eqref{FIRdef}\).

Notice also that the frequency spacing of the zeros (corresponding to the nulls in the frequency response) are at spaced at \(\small\textstyle\pm\frac{Fs}{L}\). This can be readily seen for this example, where an MA of length 8, sampled at \(\small\textstyle 500Hz\), results in a \(\small\textstyle\pm62.5Hz\) resolution.

As a final point, notice that the our efficient filter requires a delay line of length \(\small\textstyle L+1\), compared with the FIR delay line of length, \(\small\textstyle L\). However, this is a small price to pay for the computation advantage of a filter just requiring one addition and one subtraction. As such, the MA filter of Eqn. \(\small\textstyle\eqref{TF}\) presented herein is very attractive for very low power processors, such as the Arm Cortex-M0 that have been traditionally overlooked for DSP operations.

Implementation

The MA filter of Eqn. \(\small\textstyle\eqref{TF}\) may be implemented in ASN FilterScript as follows:

ClearH1; // clear primary filter from cascade

interface L = {2,32,2,4}; // interface variable definition

Main()

Num = {1,zeros(L-1),-1}; // define numerator coefficients

Den = {1,-1}; // define denominator coefficients

Gain = 1/L; // define gain

A digital filter is a mathematical algorithm that operates on a digital dataset (e.g. sensor data) in order extract information of interest and remove any unwanted information. Applications of this type of technology, include removing glitches from sensor data or even cleaning up noise on a measured signal for easier data analysis. But how do we choose the best type of digital filter for our application? And what are the differences between an IIR filter and an FIR filter?

Digital filters are divided into the following two categories:

- Infinite impulse response (IIR)

- Finite impulse response (FIR)

As the names suggest, each type of filter is categorised by the length of its impulse response. However, before beginning with a detailed mathematical analysis, it is prudent to appreciate the differences in performance and characteristics of each type of filter.

Example

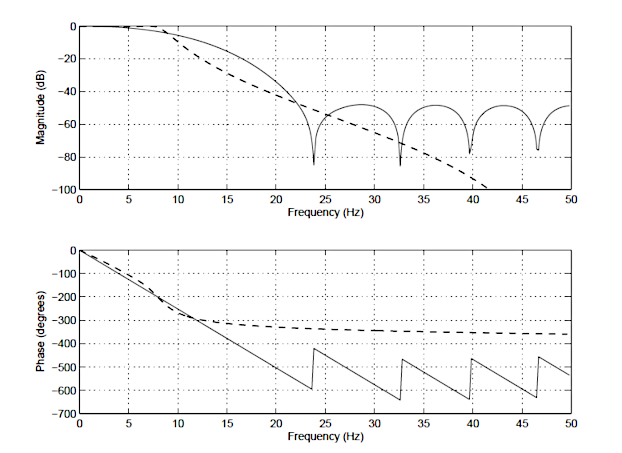

In order to illustrate the differences between an IIR and FIR, the frequency response of a 14th order FIR (solid line), and a 4th order Chebyshev Type I IIR (dashed line) is shown below in Figure 1. Notice that although the magnitude spectra have a similar degree of attenuation, the phase spectrum of the IIR filter is non-linear in the passband (\(\small 0\rightarrow7.5Hz\)), and becomes very non-linear at the cut-off frequency, \(\small f_c=7.5Hz\). Also notice that the FIR requires a higher number of coefficients (15 vs the IIR’s 10) to match the attenuation characteristics of the IIR.

These are just some of the differences between the two types of filters. A detailed summary of the main advantages and disadvantages of each type of filter will now follow.

IIR filters

IIR (infinite impulse response) filters are generally chosen for applications where linear phase is not too important and memory is limited. They have been widely deployed in audio equalisation, biomedical sensor signal processing, IoT/IIoT smart sensors and high-speed telecommunication/RF applications.

Advantages

- Low implementation cost: requires less coefficients and memory than FIR filters in order to satisfy a similar set of specifications, i.e., cut-off frequency and stopband attenuation.

- Low latency: suitable for real-time control and very high-speed RF applications by virtue of the low number of coefficients.

- Analog equivalent: May be used for mimicking the characteristics of analog filters using s-z plane mapping transforms.

Disadvantages

- Non-linear phase characteristics: The phase charactersitics of an IIR filter are generally nonlinear, especially near the cut-off frequencies. All-pass equalisation filters can be used in order to improve the passband phase characteristics.

- More detailed analysis: Requires more scaling and numeric overflow analysis when implemented in fixed point. The Direct form II filter structure is especially sensitive to the effects of quantisation, and requires special care during the design phase.

- Numerical stability: Less numerically stable than their FIR (finite impulse response) counterparts, due to the feedback paths.

FIR filters

FIR (finite impulse response) filters are generally chosen for applications where linear phase is important and a decent amount of memory and computational performance are available. They have a widely deployed in audio and biomedical signal enhancement applications. Their all-zero structure (discussed below) ensures that they never become unstable for any type of input signal, which gives them a distinct advantage over the IIR.

Advantages

- Linear phase: FIRs can be easily designed to have linear phase. This means that no phase distortion is introduced into the signal to be filtered, as all frequencies are shifted in time by the same amount – thus maintaining their relative harmonic relationships (i.e. constant group and phase delay). This is certainly not case with IIR filters, that have a non-linear phase characteristic.

- Stability: As FIRs do not use previous output values to compute their present output, i.e. they have no feedback, they can never become unstable for any type of input signal, which is gives them a distinct advantage over IIR filters.

- Arbitrary frequency response: The Parks-McClellan and ASN FilterScript’s firarb() function allow for the design of an FIR with an arbitrary magnitude response. This means that an FIR can be customised more easily than an IIR.

- Fixed point performance: the effects of quantisation are less severe than that of an IIR.

Disadvantages

- High computational and memory requirement: FIRs usually require many more coefficients for achieving a sharp cut-off than their IIR counterparts. The consequence of this is that they require much more memory and significantly a higher amount of MAC (multiple and accumulate) operations. However, modern microcontroller architectures based on the Arm’s Cortex-M cores now include DSP hardware support via SIMD (signal instruction, multiple data) that expedite the filtering operation significantly.

- Higher latency: the higher number of coefficients, means that in general a linear phase FIR is less suitable than an IIR for fast high throughput applications. This becomes problematic for real-time closed-loop control applications, where a linear phase FIR filter may have too much group delay to achieve loop stability.

- Minimum phase filters: A solution to ovecome the inherent N/2 latency (group delay) in a linear filter is to use a so-called minimum phase filter, whereby any zeros outside of the unit circle are moved to their conjugate reciprocal locations inside the unit circle. The result of the zero flipping operation is that the magnitude spectrum will be identical to the original filter, and the phase will be nonlinear, but most importantly the latency will be reduced from N/2 to something much smaller (although non-constant), making it suitable for real-time control applications.

For applications where phase is less important, this may sound ideal, but the difficulty arises in the numerical accuracy of the root-finding algorithm when dealing with large polynomials. Therefore, orders of 50 or 60 should be considered a maximum when using this approach. Although other methods do exist (e.g. the Complex Cepstrum), transforming higher-order linear phase FIRs to their minimum phase cousins remains a challenging task. - No analog equivalent: using the Bilinear, matched z-transform (s-z mapping), an analog filter can be easily be transformed into an equivalent IIR filter. However, this is not possible for an FIR as it has no analog equivalent.

Mathematical definitions

As discussed in the introduction, the name IIR and FIR originate from the mathematical definitions of each type of filter, i.e. an IIR filter is categorised by its theoretically infinite impulse response,

y(n)=\sum_{k=0}^{\infty}h(k)x(n-k)

\)

and an FIR categorised by its finite impulse response,

y(n)=\sum_{k=0}^{N-1}h(k)x(n-k)

\)

We will now analyse the mathematical properties of each type of filter in turn.

IIR definition

As seen above, an IIR filter is categorised by its theoretically infinite impulse response,

\(\displaystyle y(n)=\sum_{k=0}^{\infty}h(k)x(n-k) \)

Practically speaking, it is not possible to compute the output of an IIR using this equation. Therefore, the equation may be re-written in terms of a finite number of poles \(\small p\) and zeros \(\small q\), as defined by the linear constant coefficient difference equation given by:

y(n)=\sum_{k=0}^{q}b_k x(n-k)-\sum_{k=1}^{p}a_ky(n-k)

\)

where, \(\small a_k\) and \(\small b_k\) are the filter’s denominator and numerator polynomial coefficients, who’s roots are equal to the filter’s poles and zeros respectively. Thus, a relationship between the difference equation and the z-transform (transfer function) may therefore be defined by using the z-transform delay property such that,

\sum_{k=0}^{q}b_kx(n-k)-\sum_{k=1}^{p}a_ky(n-k)\quad\stackrel{\displaystyle\mathcal{Z}}{\longleftrightarrow}\quad\frac{\sum\limits_{k=0}^q b_kz^{-k}}{1+\sum\limits_{k=1}^p a_kz^{-k}}

\)

As seen, the transfer function is a frequency domain representation of the filter. Notice also that the poles act on the output data, and the zeros on the input data. Since the poles act on the output data, and affect stability, it is essential that their radii remain inside the unit circle (i.e. <1) for BIBO (bounded input, bounded output) stability. The radii of the zeros are less critical, as they do not affect filter stability. This is the primary reason why all-zero FIR (finite impulse response) filters are always stable.

BIBO stability

A linear time invariant (LTI) system (such as a digital filter) is said to be bounded input, bounded output stable, or BIBO stable, if every bounded input gives rise to a bounded output, as

\(\displaystyle \sum_{k=0}^{\infty}\left|h(k)\right|<\infty \)

Where, \(\small h(k)\) is the LTI system’s impulse response. Analyzing this equation, it should be clear that the BIBO stability criterion will only be satisfied if the system’s poles lie inside the unit circle, since the system’s ROC (region of convergence) must include the unit circle. Consequently, it is sufficient to say that a bounded input signal will always produce a bounded output signal if all the poles lie inside the unit circle.

The zeros on the other hand, are not constrained by this requirement, and as a consequence may lie anywhere on z-plane, since they do not directly affect system stability. Therefore, a system stability analysis may be undertaken by firstly calculating the roots of the transfer function (i.e., roots of the numerator and denominator polynomials) and then plotting the corresponding poles and zeros upon the z-plane.

An interesting situation arises if any poles lie on the unit circle, since the system is said to be marginally stable, as it is neither stable or unstable. Although marginally stable systems are not BIBO stable, they have been exploited by digital oscillator designers, since their impulse response provides a simple method of generating sine waves, which have proved to be invaluable in the field of telecommunications.

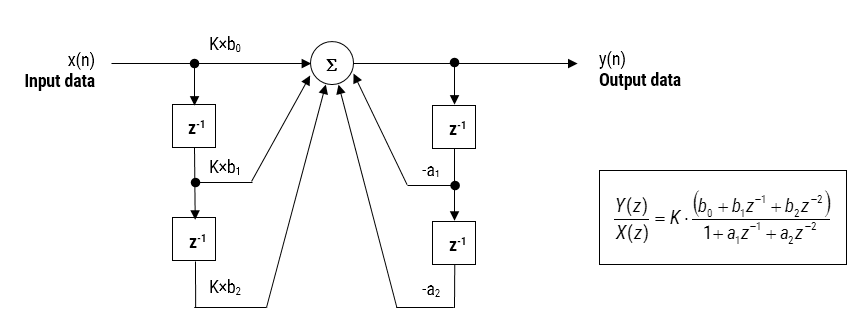

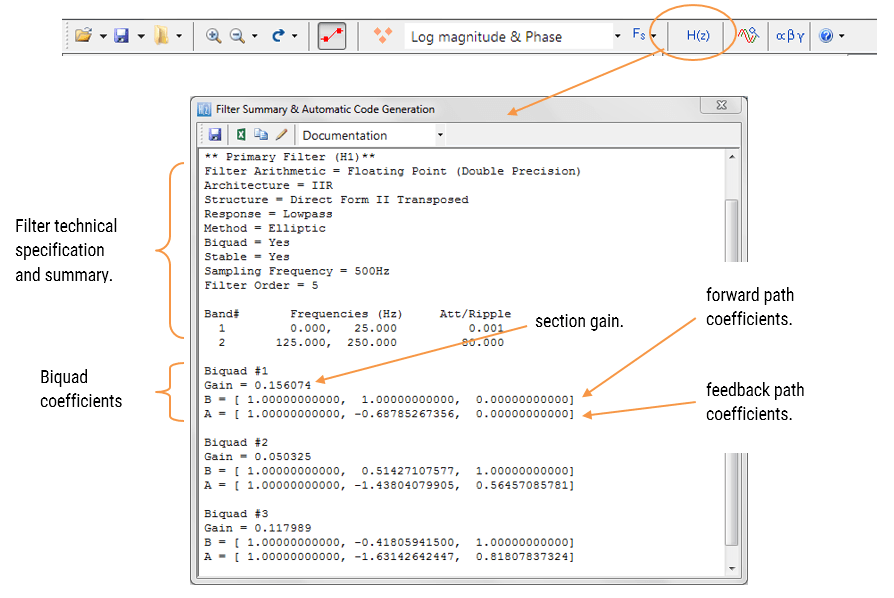

Biquad IIR filters

The IIR filter implementation discussed herein is said to be biquad, since it has two poles and two zeros as illustrated below in Figure 2. The biquad implementation is particularly useful for fixed point implementations, as the effects of quantization and numerical stability are minimised. However, the overall success of any biquad implementation is dependent upon the available number precision, which must be sufficient enough in order to ensure that the quantised poles are always inside the unit circle.

Figure 2: Direct Form I (biquad) IIR filter realization and transfer function.

Analysing Figure 2, it can be seen that the biquad structure is actually comprised of two feedback paths (scaled by \(\small a_1\) and \(\small a_2\)), three feed forward paths (scaled by \(\small b_0, b_1\) and \(\small b_2\)) and a section gain, \(\small K\). Thus, the filtering operation of Figure 1 can be summarised by the following simple recursive equation:

\(\displaystyle y(n)=K\times\Big[b_0 x(n) + b_1 x(n-1) + b_2 x(n-2)\Big] – a_1 y(n-1)-a_2 y(n-2)\)

Analysing the equation, notice that the biquad implementation only requires four additions (requiring only one accumulator) and five multiplications, which can be easily accommodated on any Cortex-M microcontroller. The section gain, \(\small K\) may also be pre-multiplied with the forward path coefficients before implementation.

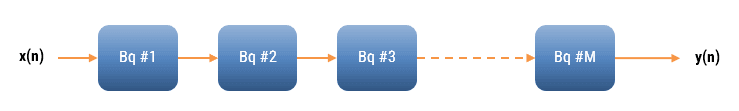

A collection of Biquad filters is referred to as a Biquad Cascade, as illustrated below.

The ASN Filter Designer can design and implement a cascade of up to 50 biquads (Professional edition only).

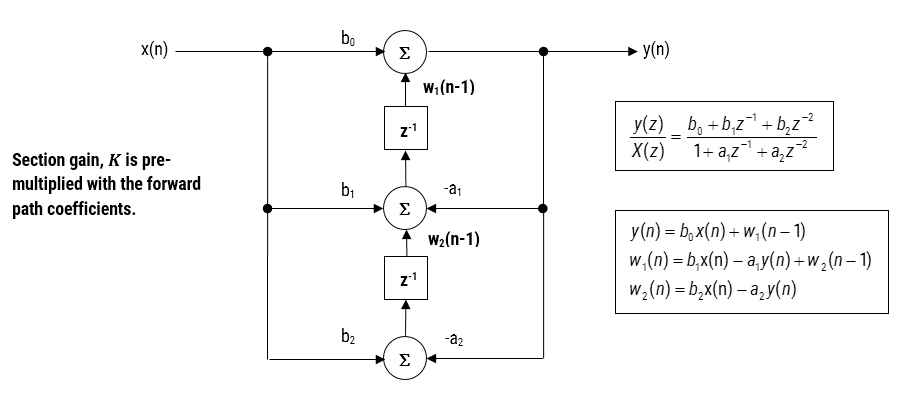

Floating point implementation

When implementing a filter in floating point (i.e. using double or single precision arithmetic) Direct Form II structures are considered to be a better choice than the Direct Form I structure. The Direct Form II Transposed structure is considered the most numerically accurate for floating point implementation, as the undesirable effects of numerical swamping are minimised as seen by analysing the difference equations.

Figure 3 – Direct Form II Transposed strucutre, transfer function and difference equations

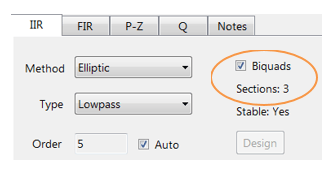

The filter summary (shown in Figure 4) provides the designer with a detailed overview of the designed filter, including a detailed summary of the technical specifications and the filter coefficients, which presents a quick and simple route to documenting your design.

The ASN Filter Designer supports the design and implementation of both single section and Biquad (default setting) IIR filters.

FIR definition

Returning the IIR’s linear constant coefficient difference equation, i.e.

y(n)=\sum_{k=0}^{q}b_kx(n-k)-\sum_{k=1}^{p}a_ky(n-k)

\)

Notice that when we set the \(\small a_k\) coefficients (i.e. the feedback) to zero, the definition reduces to our original the FIR filter definition, meaning that the FIR computation is just based on past and present inputs values, namely:

y(n)=\sum_{k=0}^{q}b_kx(n-k)

\)

Implementation

Although several practical implementations for FIRs exist, the direct form structure and its transposed cousin are perhaps the most commonly used, and as such, all designed filter coefficients are intended for implementation in a Direct form structure.

The Direct form structure and associated difference equation are shown below. The Direct Form is advocated for fixed point implementation by virtue of the single accumulator concept.

\(\displaystyle y(n) = b_0x(n) + b_1x(n-1) + b_2x(n-2) + …. +b_qx(n-q) \)

The recommended (default) structure within the ASN Filter Designer is the Direct Form Transposed structure, as this offers superior numerical accuracy when using floating point arithmetic. This can be readily seen by analysing the difference equations below (used for implementation), as the undesirable effects of numerical swamping are minimised, since floating point addition is performed on numbers of similar magnitude.

\(\displaystyle \begin{eqnarray}y(n) & = &b_0x(n) &+& w_1(n-1) \\ w_1(n)&=&b_1x(n) &+& w_2(n-1) \\ w_2(n)&=&b_2x(n) &+& w_3(n-1) \\ \vdots\quad &=& \quad\vdots &+&\quad\vdots \\ w_q(n)&=&b_qx(n) \end{eqnarray}\)

Implementing your filter on an Arm Cortex-M processor

Although a few processor technologies exist for microcontrollers (e.g. RISC-V, Xtensa, MIPS), over 90% of the microcontrollers used in the smart product market are powered by so-called Arm Cortex-M processors that offer a combination of high algorithmic performance, low-power and security. The Arm Cortex-M4 is a very popular choice with several silicon vendors (including ST, TI, NXP, ADI, Nordic, Microchip, Renesas), as it offers DSP (digital signal processing) functionality traditionally found in more expensive devices and is low-power.

Filtering libraries and support

Arm and ASN provide developers with extensive easy-to-use tooling and tried and tested software libraries used internationally by tens of thousands of developers.

The Arm CMSIS-DSP software framework is interesting as it provides IoT developers with a rich collection of fast mathematical and vector functions, interpolation functions, digital filtering (FIR/IIR) and adaptive filtering (LMS) functions, motor control functions (e.g. PID controller), complex math functions and supports various data types, including fixed and floating point. The important point to make here is that all of these functions have been optimised for Arm Cortex-M processors, allowing you to focus on your application rather than worrying about optimisation.

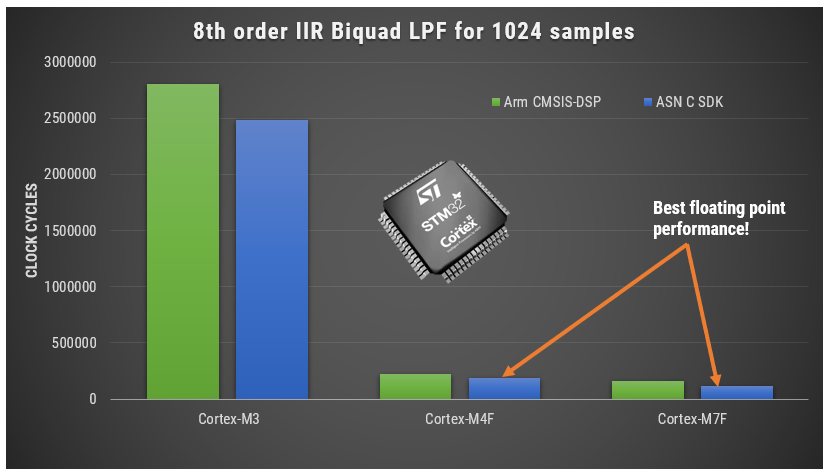

Despite the broad functionality, the CMSIS-DSP library is somewhat limited for filters, so the flexible ASN DSP filtering library can be used instead, which supports the higher numerical accuracy Direct Form Transposed FIR filter structure and single section IIR filters. A benchmark of ASN’s floating point application-specific DSP filtering library versus Arm’s CMSIS-DSP library is shown below for three types of Arm cores.

As seen, the performance of the ASN library is slightly faster by virtue of the application-specific nature of the implementation. The C code is automatically generated from the ASN Filter Designer tool.

What have we learned?

Digital filters are divided into the following two categories:

- Infinite impulse response (IIR)

- Finite impulse response (FIR)

IIR (infinite impulse response) filters are generally chosen for applications where linear phase is not too important and memory is limited. They have been widely deployed in audio equalisation, biomedical sensor signal processing, IoT/AIoT smart sensors and high-speed telecommunication/RF applications.

FIR (finite impulse response) filters are generally chosen for applications where linear phase is important and a decent amount of memory and computational performance are available. They have a widely deployed in audio and biomedical signal enhancement applications.

ASN Filter Designer provides engineers with everything they need to design, experiment and deploy complex IIR and FIR digital filters for a variety of IoT sensor measurement applications. These advantages coupled with automatic C code generation with ASN’s DSP filtering library functionality allow engineers to design, validate and then deploy their designs to an Arm Cortex-M processor within hours rather than more traditional routes that could take days.

Author

-

Sanjeev is a RTEI (Real-Time Edge Intelligence) visionary and expert in signals and systems with a track record of successfully developing over 26 commercial products. He is a Distinguished Arm Ambassador and advises top international blue chip companies on their AIoT/RTEI solutions and strategies for I5.0, telemedicine, smart healthcare, smart grids and smart buildings.

View all posts

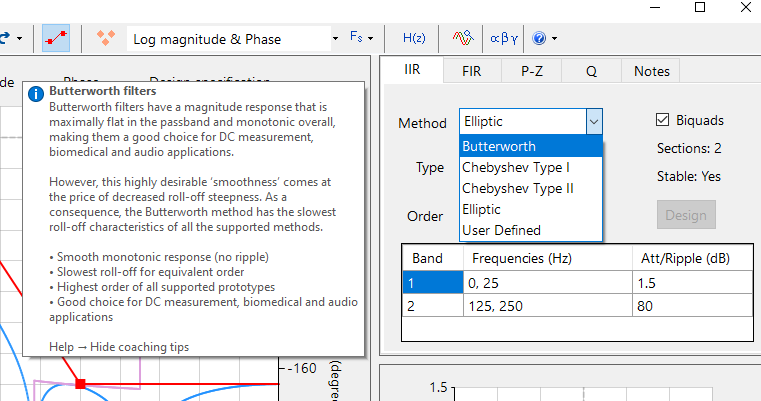

UI experience 2020 pack

After downloading the ASN Filter Designer, most people just want to play with the tool, in order to get a feeling of whether it works for them. But how do you get started with the ASN Filter Designer? Based on some great user feedback, ASNFD v4.4 now comes with the UI experience 2020 pack. This pack includes detailed coaching tips, an enhanced user experience and step-by-step instructions to get you started with your design.

A quick overview of the ASN Filter Designer v4.4 is given below, and we’re sure that you’ll agree that it’s an awesome tool for DSP IIR/FIR digital filter design!

The ASN Filter Designer has a fast, intuitive user interface. Interactively design, validate and deploy your digital filter within minutes rather than hours. However, getting started with DSP Filter Design can be difficult, especially when you don’t have deep knowledge of digital signal processing. Most people just want to experiment with a tool to get a feeling whether it works for them (sure, there are tutorials and videos). But where do you start?

Start experimenting with filter design immediately

That’s why we have developed the UI Experience 2020 pack. Based on user feedback, we’ve created detailed tooltips and animations of key functionality. Within minutes, you’ll get a kick-start into functionalities such as chart zooming, panning and design markers.

Coaching tips, enhanced user experience, step-by-step instructions

Based on user feedback, the UI Experience 2020 pack includes:

- Extensive coaching tips

- Detailed explanations of design methods and types of filters

- Enhanced user experience:

- cursors

- animations

- visual effects

- Short cuts to detailed worked solutions, tutorials and step-by-step instructions

Feedback from the user community has been very positive indeed! By providing detailed tooltips and animations of key functionality, the initial hurdle of designing a filter with your desired specifications has now been significantly simplified.

So start with the ASN Filter Designer right away, and cut your development costs by up to 75%!

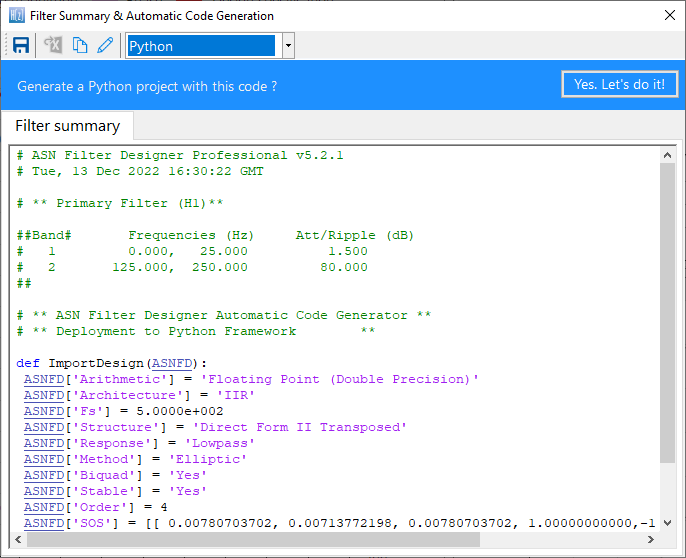

For many IoT sensor measurement applications, an IIR or FIR filter is just one of the many components needed for an algorithm. This could be a powerline interference canceller for a biomedical application or even a simpler DC loadcell filter. In many cases, it is necessary to integrate a filter into a complete algorithm in another domain. ASN Filter Designer’s automatic code generator greatly simlifies exporting to Python.

Python is a very popular general-purpose programming language with support for numerical computing, allowing for the design of algorithms and performing data analysis. The language’s numpy and signal add-on modules attempt to bridge the gap between numerical algorithmic languages, such as Matlab and more traditional programming languages, such as C/C++. As such, it is much more appealing to experienced programmers, who are used to C/C++ data types, syntax and functionality, rather than Matlab’s scripting language that is more aimed at mathematicans developing algorithmic concepts.

ASN Filter Designer automatic code generator for Python

The ASN Filter Designer greatly simplifies exporting a designed filter to Python via its automatic code generator. The code generator supports all aspects of the ASN Filter Designer, allowing for a complete design comprised of H1, H2 and H3 filters and math operators to be fully integrated with an algorithm in Python.

The Python code generator can be accessed via the filter summary options (as shown on the right). Selecting this option will automatically generate a Python .py design file based on the current design settings.

Version 5 of the tool has a completely revamped filter summary UI, and now includes built in AI to analyse the filter cascade for any potential problems.

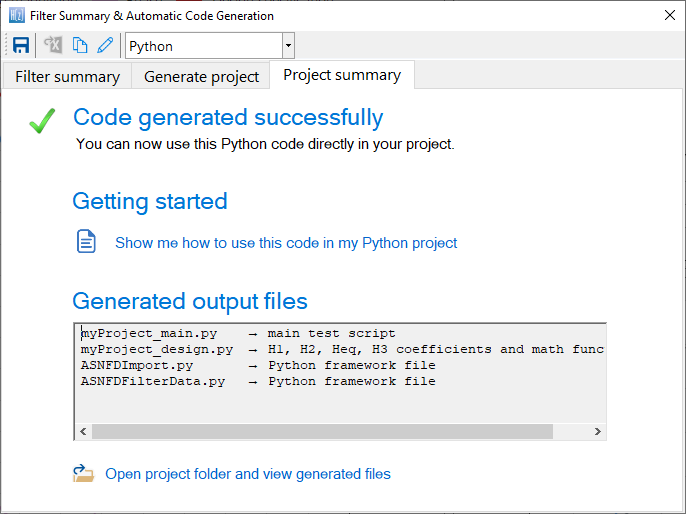

The project wizard bundles all of the necessary SDK framework files needed to run the designed filter cascade without the need for any other dependencies or 3rd party plugins.

The framework supports both Real and Complex filters in floating point only, and is built on ASN IP blocks, rather than Python’s signal module, which was seen to struggle with managing complex data. Thus, in order to expedite algorithm development with the framework, the following three demos are provided:

ASNFDPythonDemo: main demo file with various examplesRMSmeterDemo: An RMS amplitude powerline meter demoEMGDataDemo: An EMG biomedical demo with a HPF, 50Hz notch filter and averaging

An example of the summary of all of generated files (including the framework files) is shown below.

These files can be used directly in your Python project.

Drones and DC motor control – How the ASN Filter Designer can save you a lot of time and effort

Drones are one of the golden nuggets in IoT. No wonder, they can play a pivotal role in congested cities and far away areas for delivery. Further, they can be a great help to give an overview of a large area or places which are difficult or dangerous to reach. However, most of the technology is still in its experimental stage.

Because drones have a lot of sensors, Advanced Solutions Nederland did some research on how drone producing companies have solved questions regarding their sensor technology, especially regarding DC motor control.

Until now: solutions developed with great difficulty

We found out that most producers spend weeks or even months on finding solutions for their sensor technology challenges. With the ASN Filter Designer, he/she could have come to a solution within days or maybe even hours. Besides, we expect that the measurement would be better too.

The biggest time coster is that until now algorithms were developed by handwork, i.e. they were developed in a lab environment and then tested in real-life. With the result of the test, the algorithm would be tweaked again until the desired results were reached. However, yet another challenge stems from the fact that a lab environment is where testing conditions are stable, so it’s very hard to make models work in real life. These steps result in rounds and rounds of ‘lab development’ and ‘real life testing’ in order to make any progress -which isn’t ideal!

How the ASN Filter Designer can help save a lot of time and effort

The ASN Filter Designer can help a lot of time in the design and testing of algorithms in the following ways:

- Design, analyse and implement filters for drone sensor applications with real-time feedback and our powerful signal analyser.

- Design filters for speed and positioning control for sensorless BLDC (brushless DC) motor applications.

- Speed up deployment to Arm Cortex-M embedded processors.

Real-time feedback and powerful signal analyser

One of the key benefits of the ASN Filter Designer and signal analyser is that it gives real-time feedback. Once an algorithm is developed, it can easily be tested on real-life data. To analyse the real-life data, the ASN Filter Designer has a powerful signal analyser in place.

Design and analyse filters the easy way

You can easily design, analyse and implement filters for a variety of drone sensor applications, including: loadcells, strain gauges, torque, pressure, temperature, vibration, and ultrasonic sensors and assess their dynamic performance in real-time for a variety of input conditions. With the ASN Filter Designer, you don’t have do to any coding yourself or break your head with specifications: you just have to draw the filter magnitude specification and the tool will calculate the coefficients itself.

Speed up deployment

Perform detailed time/frequency analysis on captured test datasets and fine-tune your design. Our Arm CMSIS-DSP and C/C++ code generators and software frameworks speed up deployment to a DSP, FPGA or micro-controller.

An example: designing BLDC motor control algorithms

BLDC (brushless DC) BLDC motors have found use in a variety of application areas, including: robotics, drones and cars. They have significant advantages over brushed DC motors and induction motors, such as: better speed-torque characteristics, high reliability, longer operating life, noiseless operation, and reduction of electromagnetic interference (EMI).

One advantage of BLDC motor control compared to standard DC motors is that the motor’s speed can be controlled very accurately using six-step commutation, making it a good choice for precision motion applications, such as robotics and drones.

Sensorless back-EMF and digital filtering

For most applications, monitoring of the back-EMF (back-electromotive force) signal of the unexcited phase winding is easier said than done, since it has significant noise distortion from PWM (pulse width modulation) commutation from the other energised windings. The coupling between the motor parameters, especially inductances, can induce ripple in the back-EMF signal that is synchronous with the PWM commutation. As a consequence, this induced ripple on the back EMF signal leads to faulty commutation. Thus, the measurement challenge is how to accurately measure the zero-crossings of the back-EMF signal in the presence of PWM signals?

A standard solution is to use digital filtering, i.e. IIR, FIR or even a median (majority) filter. However, the challenge for most designers is how to find the best filter type and optimal filter specification for the motor under consideration.

The solution

The ASN Filter Designer allows engineers to work on speed and position sensorless BLDC motor control applications based on back-EMF filtering to easily experiment and see the filtering results on captured test datasets in real-time for various IIR, FIR and median (majority filtering) digital filtering schemes. The tool’s signal analyser implements a robust zero-crossings detector, allowing engineers to evaluate and fine-tune a complete sensorless BLDC control algorithm quickly and simply.

So, if you have a measurement problem, ask yourself:

Can I save time and money, and reduce the headache of design and implementation with an investment in new tooling?

Our licensing solutions start from just 125 EUR for a 3-month licence.

Find out what we can do for you, and learn more by visiting the ASN Filter Designer’s product homepage.

The moving average (MA) filter is perhaps one of the most widely used FIR filters due to its conceptual simplicity and ease of implementation. As seen in the diagram below, notice that the filter doesn’t require any multiplications, just additions and a delay line, making it very suitable for many extreme low-power embedded devices with basic computational capabilities.

However, despite its simplicity, the moving average filter is optimal for reducing random noise while retaining a sharp step response, making it a versatile building block for smart sensor signal processing applications.

A moving average filter of length \(L\) for an input signal \(x(n)\) may be defined as follows:

\(y(n)=\large{\frac{1}{L}}\normalsize{\sum\limits_{k=0}^{L-1}x(n-k)}\) for \(\normalsize{n=0,1,2,3….}\)

Where, a simple rule of thumb states that the amount of noise reduction is equal to the square-root of the number of points in the average. For example, an MA of length 9 will result in a factor 3 noise reduction.

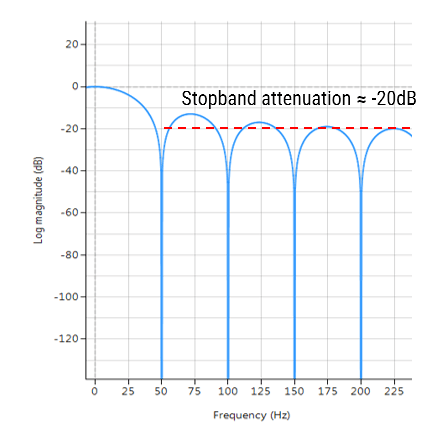

Frequency response of an MA filter of length 9. Notice the poor stopband attentuation at around -20dB.

Frequency response of an MA filter of length 9. Notice the poor stopband attentuation at around -20dB.

Advantages

- Most commonly used digital lowpass filter.

- Optimal for reducing random noise while retaining a sharp step response.

- Good smoother (time domain).

- Unity valued filter coefficients, no MAC (multiply and accumulate) operations required.

- Conceptually simple to implement.

Disadvantages

- Inflexible frequency response: nudging a conjugate zero pair results in non-unity coefficients.

- Poor lowpass filter (frequency domain): slow roll-off and terrible stopband attenuation characteristics.

Implementation

The MA filter may be implemented in ASN FilterScript as follows:

ClearH1; // clear primary filter from cascade

Main();

Hd=movaver(8,"symbolic"); // design an 8th order MA

Num = getnum(Hd); // define numerator coefficients

Den = {1}; // define denominator coefficients

Gain = getgain(Hd); // define gain

A more computationally efficient implementation of the MA filter is discussed here.

Further reading

- Understanding Digital Signal Processing, Chapter 5, R. G. Lyons

- The Scientist and Engineer’s Guide to Digital Signal Processing, Chapter 15, Steven W. Smith

Advanced Solutions Nederland B.V.

Lipperkerstraat 146

751DD Enschede

The Netherlands

General enquiries: info@advsolned.com

Technical support: support@advsolned.com

Sales enquiries: sales@advsolned.com

© 2026 Advanced Solutions Nederland B.V.

Privacy Policy | Disclaimer